# EC210 PCIバス・マスター/ターゲット・メガファンクション

Solution Brief 19

April 1997, ver. 1

## ターゲット・アプリケーション： 機能

バス・インターフェース

ファミリ：FLEX 10K

ベンダ：

Eureka Technology

Eureka Technology Inc.

4962 El Camino Real #108

Los Altos, CA 94022

USA

Tel. (415) 960-3800

Fax (415) 960-3805

E-mail info@eurekatech.com

PCI-SIG (Peripheral Component Interconnect Special Interest Group)のPCIローカルバス仕様に完全準拠。

PCIバス・マスター/ターゲットの全機能を実現。

アルテラ FLEX® 10K デバイス・アーキテクチャに最適化。

スロー出力イネーブル・コントロール機能を持つデバイスに最適化。

すべてのPCIコンフィギュレーション・レジスタをサポート。

PCIバス・マスターの多様なタイプに適応した効率的なバックエンド・インターフェース。

コントロール・レジスタのプログラムが可能なターゲット機能を実現。

ターゲット・リトライ、ディスコネクト、ターゲット・アポートの各信号をサポート。

ターゲット・リトライとディスコネクト信号による自動転送再開機能。

## 概要

EC210 PCIバス・マスター/ターゲット・メガファンクションは、PCIバスとシンプルなX86タイプのバックエンド・デバイスとの間を効率良くインターフェースするために設計されたバス・インターフェース・ユニットです。このメガファンクションは双方向PCIバスのトランシスレータとして動作し、バックエンド・デバイスがPCIメモリやI/Oインターフェースにアクセスするために必要なすべてのデータ転送を実行します。このメガファンクションへのアクセスは、バックエンド・デバイスを通してPCIバス・マスター(例えば、ビデオ・コプロセッサやDMAコントローラ)によってイニシエイトされます。

このメガファンクションはバス・マスターがPCIバスをアクセスするときに必要となるすべてのデータ転送を実行します。最高のメモリ・バンド幅が提供されるようにするために、このメガファンクションは双方向の転送でゼロ・ウェイト・ステートを含むシングルおよびバースト・モードのデータ転送をサポートしています。PCI上のすべてのデータ転送はバック・エンド・デバイスを通じてアクセスされます。

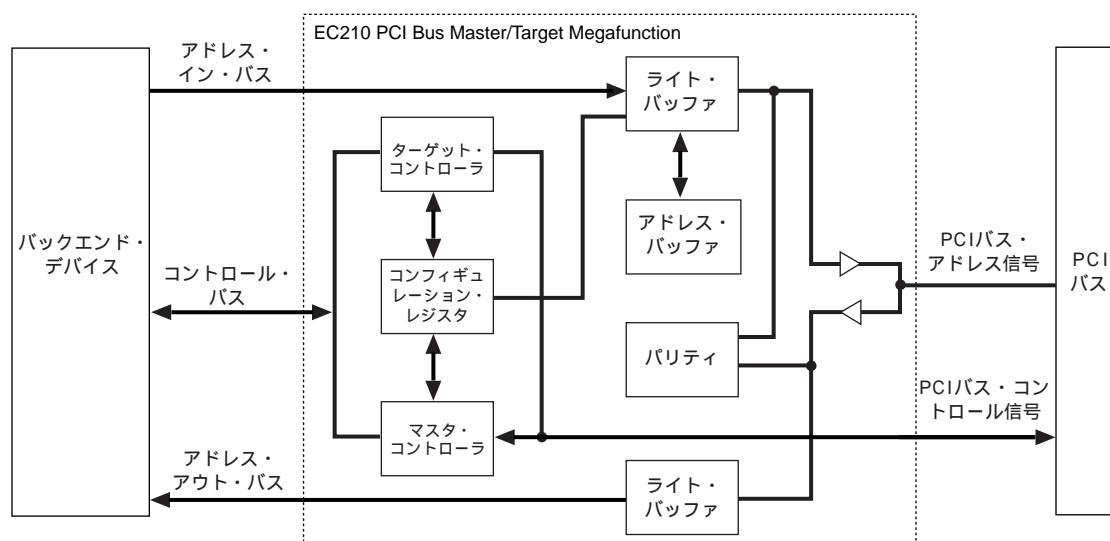

図1はメガファンクションのブロック図とその双方向動作を示したものです。

図1 EC210 PCIバス・マスター/ターゲット・メガファンクション

### 機能説明

EC210、PCIバス・マスタ / ターゲットのメガファンクションは双方方向トランスレータとして動作するため、別のマスタ（またはホスト）がバックエンド・デバイスに逆方向からデータを読み出したり書き込んだり、DMAコントロール・レジスタにプログラムするような処理を実行することができます。バックエンド・デバイスの機能を有するDAMコントローラのようなバス・マスタは、PCIバスに対するデータ転送を簡単に開始させることができます。バックエンド・デバイス上にDMAコントローラがある場合は、このメガファンクションは高速のバス・リクエストやアービトレーションをサポートすることによって、転送のレイテンシを最小に抑えることができます。

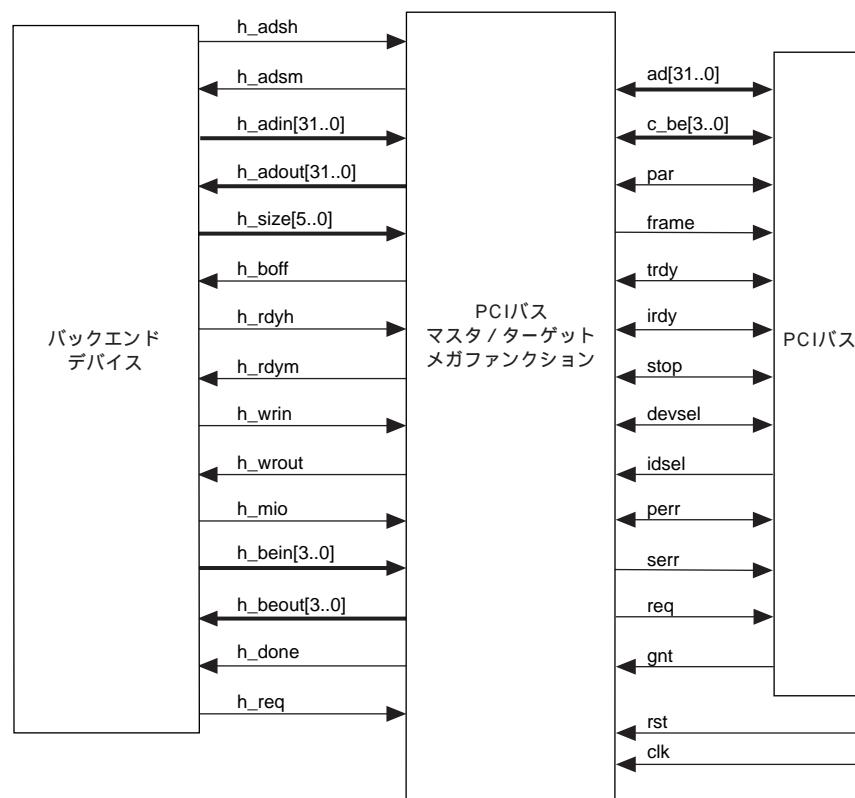

図2には、機能ごとに分類されたEC210 PCIバス・マスタ / ターゲット・メガファンクションの信号が示されています。

図2 EC210 PCIバス・マスタ / ターゲット・メガファンクションの信号

表1はEC210 PCIバス・マスタ / ターゲット・メガファンクションとPCIバスをインターフェースする信号を解説したものです。

| 表1 EC210 PCIバス・マスタ / ターゲット・メガファンクションとPCIバスとのインターフェース信号 |     |                                                                                                                                     |

|--------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| 信号名                                                    | タイプ | 説明                                                                                                                                  |

| gnt                                                    | 入力  | グラント信号。マスタがPCIバスへのアクセスを認められたことを示す信号。                                                                                                |

| idsel                                                  | 入力  | イニシャライゼーション・デバイス・セレクト信号。この信号はコンフィギュレーション・リードやライトの動作中に、チップ・セレクトとして使用される。                                                             |

| clk                                                    | 入力  | システム・クロック。                                                                                                                          |

| rst                                                    | 入力  | システム・リスタート信号。                                                                                                                       |

| req                                                    | 出力  | PCIバス・リクエスト信号。マスタがPCIバス上での権利を獲得するときに、この信号をアサートする。                                                                                   |

| serr                                                   | 出力  | システム・エラー信号。アドレス・パリティ・エラーや特殊なサイクル・パリティ・エラーをリポートする信号。コンフィギュレーション・コマンドにより許可された場合にのみ、マスタまたはターゲットによってもアサートできる。                           |

| frame                                                  | 出力  | サイクル・フレーム信号。マスタはトランズアクションの開始と実行中を表示するときにこの信号を出力する。frameがアサートされているときはデータ転送が処理中であることを示し、ディアサートされているときはデータ転送の最終フェーズであることを示す。           |

| ad[31..0]                                              | I/O | アドレスとデータ信号はPCIバスの同一ピン上でマルチプレクスされる。PCIバスの処理は、1つのアドレス・フェーズに続いて1つまたは複数のデータ・フェーズによって構成される。このメガファンクションでは、リード / ライトのバースト・データ転送がサポートされている。 |

| c_be[3..0]                                             | I/O | バス・コマンドとバイト・イネーブル信号がPCIバスの同一ピン上でマルチプレクスされる。c_be[3..0]は、アドレス・フェーズのトランズアクション処理中にバス・コマンドを発行し、トランズアクション中のデータ・フェーズではバイト・イネーブル信号を発行する。    |

| devsel                                                 | I/O | デバイス・セレクト信号。マスタが対応するアドレスをデコードするとき、ターゲットがこの信号をアサートする。devselが入力信号として扱われる場合は、このdevselがPCIバス上で選択されているデバイスを表示。                           |

| irdy                                                   | I/O | イニシエイタ・レディ信号。マスタがデータ転送を終了したことを示す信号。irdyはtrdyと共にデータ転送の完了を表示する信号として使用される。                                                             |

| par                                                    | I/O | パリティ信号。ad[31..0]とc_be[3..0]信号との偶数パリティ信号。この信号は、アドレスとライト・トランズアクション時のマスタか、すべてのリード・トランズアクション時のターゲットにより駆動される。                            |

| perr                                                   | I/O | パリティ・エラー信号。アドレスまたはデータのトランズアクション中にパリティ・エラーが検出されると、マスタまたはターゲットによってこの信号がアサートされる。                                                       |

| stop                                                   | I/O | マスタ・トランズアクションを停止するために、ターゲットがアサートする信号。                                                                                               |

| trdy                                                   | I/O | ターゲット・レディ信号。ターゲットが現在のデータ・フェーズ・トランズアクションを完了することを表示する信号。trdyはirdyと共にデータ転送の終了を表示する信号として使用される。                                          |

表2は、EC210 PCIバス・マスタ / ターゲット・メガファンクションとバックエンド・デバイスとのインターフェースする信号を解説したものです。

| 表2 EC210 PCIバス・マスタ / ターゲット・メガファンクションとバックエンド・デバイスとのインターフェース信号(1/2) |     |                                                                                                                                                         |

|-------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 信号名                                                               | タイプ | 説明                                                                                                                                                      |

| h_adin[31..0]                                                     | 入力  | アドレスとデータがマルチプレクスされているPCIバス信号。この信号はターゲットからマスタに対して出力される。この信号は、PCIバスがライト・トランズアクションの実行中にアドレス / データの転送中であることを示し、またコントロール・レジスタへのリード・トランズアクション中にデータ転送であることを示す。 |

| h_adsh                                                            | 入力  | アドレス・ストローブ信号。ターゲットがPCIバス上のリード / ライト転送を行うときに、この信号をアサートする。                                                                                                |

| h_bein[3..0]                                                      | 入力  | バイト・イネーブル・バス信号。この信号はPCIバスのリード / ライト・サイクルでアクティブなバイト数を表示。                                                                                                 |

| h_mio                                                             | 入力  | メモリ、I/Oセレクト信号。アドレス・スペースのメモリ（ハイ・レベル）か、I/O（ロー・レベル）を選択する信号。                                                                                                |

| h_rdyh                                                            | 入力  | ライト・トランズアクション時に、ターゲットのコントロール・レジスタがPCIバス上のデータを受け入れたことを示す信号。リード・トランズアクションでは、ターゲットのコントロール・レジスタがデータ転送を処理したことを示す。                                            |

| h_req                                                             | 入力  | ホスト・リクエスト信号。次のクロック・サイクルで転送が開始されることを示すh_adsh信号がアサートされる1クロック・サイクル前に、ターゲットがこの信号をアサートすることができる。この信号によって、PCIインターフェースは最小のバス遅延でリクエスト信号をアサートできるようになる。            |

表2 EC210 PCIバス・マスター/ターゲット・メガファンクションとバックエンド・デバイスとのインターフェース信号(2/2)

| 信号名            | タイプ | 説明                                                                                                                                                                                                 |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| h_size[5..0]   | 入力  | バースト転送の長さを示す信号。この信号の値が000001になっている場合は、単一転送を示す。信号の値がすべて0の場合は、64ビットの転送長を示す。他の値の場合は、それぞれの転送長さを示す。転送長がターゲットのアドレス空間を超えないようにする必要がある。                                                                     |

| h_wrin         | 入力  | バックエンド・デバイスがPCIバス・マスターへのリード(ロー・レベル)またはライト(ハイ・レベル)トランズアクションを表示するために生成する信号。                                                                                                                          |

| h_adsm         | 出力  | マスターがリード/ライト・トランズアクションを行うために、コントロール・レジスタへのアクセスを要求するときにアサートする信号。                                                                                                                                    |

| h_adout[31..0] | 出力  | アドレスとデータがマルチプレクスされたPCIバス信号。この信号はマスターからターゲットに対して出力される。コントロール・レジスタへのライト・トランズアクション時にアドレス/データが転送中であること、およびPCIバスのリード・トランズアクション時にデータが転送中であることを示す。                                                        |

| h_beout[3..0]  | 出力  | バイト・イネーブル・バス信号。コントロール・レジスタへのアクセスを示す信号。                                                                                                                                                             |

| h_boff         | 出力  | バック・オフ信号。この信号がh_done信号と同時にアサートされると、異常な終了がPCIバス上に発生し、実行中の転送が中止される。h_boffのみがアサートされたときは、PCIバス・リクエスト入力信号がペンディングになっているか、マスターがbusyの状態になっていることを示す。PCIバス・リクエストがペンディングにされているとき、ターゲットは転送リクエストをアポートしなければならない。 |

| h_done         | 出力  | 終了を示す出力。この信号はPCIトランズアクションが完了したときにアサートされる。ライト動作の場合は、最後のデータがライト・バッファに書き込まれると、すぐにh_rdym信号がアサートされ、PCIバス・データ転送が完了したときにh_done信号がアサートされる。                                                                 |

| h_rdym         | 出力  | ライト・トランズアクション時に、このメガファンクションがPCIバスのデータを取り込んだことを示す信号。リード・トランズアクションでは、このメガファンクションがデータ転送を処理したことを示す信号となる。                                                                                               |

| h_wrout        | 出力  | この信号はコントロール・レジスタのアクセス・サイクルの期間に有効となる。PCIのバス・マスターがこの信号を生成し、コントロール・レジスタ・アクセスがリードの場合はロー・レベル、ライトの場合はハイ・レベルとなる。                                                                                          |

### オプション機能

数種類のPCIバス・マスターのオプションがEureka Technology社から提供されています。その中には、ダイレクトFIFO(First-in First-out)インターフェース、メモリまたはI/Oマッピング64ビットへのバス拡張、ホスト・ブリッジなどがあります。これらオプションの詳細については、Eureka Technology社へお問い合わせください。

### 使用効率

表3にEC210 PCIバス・マスター/ターゲット・メガファンクションの標準的なデバイス使用効率を示します。

| 表3 標準的なデバイス・リソースの使用効率 |                   |          |                       |

|-----------------------|-------------------|----------|-----------------------|

| 機能                    | クロック( $f_{MAX}$ ) | ロジック・セル数 | エンベデッド・アレイ・ブロック(EAB)数 |

| マスター/ターゲット            | 33MHz             | 650      | 0                     |

### 参考文献

PCI Special Interest Group. PCI ローカル・バス仕様書 Rev. 2.1. Hillsboro, Oregon: PCI Special Interest Group, 1995.

## 日本アルテラ株式会社

〒163-04 東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL.03-3340-9480FAX.03-3340-9487

Copyright© 1997 Altera Corporation. Altera MPP, FLEX, FLEX 10KはAltera Corporationの米国および該当各国におけるtrademarkまたはservice markです。この資料はAltera Corporationが発行した資料を日本語化したもので、アルテラが保証する内容は英文オリジナルのものです。ここに記載された内容は予告なく変更されることがあります。Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.